Trong bối cảnh Mỹ hạn chế xuất khẩu chip dành cho AI và siêu máy tính, các nhà khoa học Trung Quốc đã tìm ra một giải pháp sáng tạo: thay vì chạy đua làm chip nhỏ hơn, họ tạo ra các bộ xử lý có kích thước lớn bằng cả tấm wafer.

Giải pháp này được gọi là “Big Chip”, với những bộ xử lý kích thước lớn được phát triển bởi đội ngũ đến từ Viện Công nghệ Thông tin, thuộc Học viện Khoa học Trung Quốc, dẫn đầu bởi giáo sư phó Xu Haobo và giáo sư Sun Ninghui. Cách tiếp cận này được gọi là Wafer-Scale Integration (WSI).

Bộ xử lý Zhejiang, phiên bản đầu tiên của “Big Chip”, có diện tích lên đến hàng nghìn mm2 bao gồm 16 chiplet với 256 lõi và có khả năng mở rộng lên đến 100 chiplet, tương đương với 1.600 lõi.

Thay vì được chế tạo trên các quy trình hiện đại nhất hiện nay, Zhejiang được thiết kế và chế tạo trên quy trình CMOS 22nm – quy trình công nghệ nằm trong tầm tay của năng lực đúc chíp Trung Quốc. Tuy vậy, bộ xử lý này vẫn hứa hẹn sẽ nâng cao hiệu suất cho tính toán hiệu năng cao (HPC) và đào tạo AI thế hệ mới.

Giải pháp Big Chip này sẽ mang đến 2 ưu điểm. Đầu tiên, nhờ kích thước lớn của nó, mỗi bộ xử lý có thể chứa được nhiều bóng bán dẫn hơn so với một vi chip thông thường được chế tạo bởi công nghệ hiện tại. Theo ước tính của các nhà khoa học, mỗi Big Chip có thể chứa đến một nghìn tỷ bóng bán dẫn.

Thứ hai, mỗi Big Chip này sẽ có hàng loạt die chip chức năng kết hợp với nhau. Hàng loạt kỹ thuật chế tạo bán dẫn mới sẽ được sử dụng để tích hợp các die chip được trong một chip cỡ lớn.

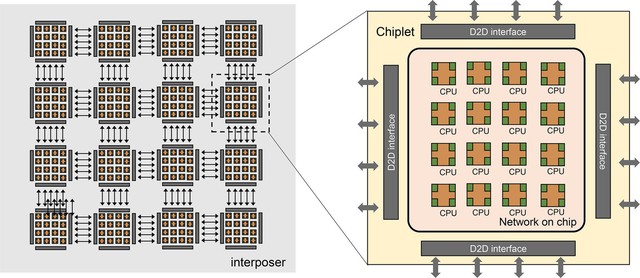

Sơ đồ cho kiến trúc liên kết bên trong con chip Zhejiang

Theo Han Yinhe, tác giả đầu tiên của nghiên cứu này, cho biết trong tài liệu: “Khi Định luật Moore ngày càng đi đến hồi kết, việc tạo ra các chip hiệu năng cao thông qua gia tăng số lượng bóng bán dẫn đang ngày càng khó khăn hơn. Để cải thiện hiệu năng, gia tăng diện tích chip nhằm tích hợp các bóng bán dẫn sẽ là một cách tiếp cận khả thi.”

Do các Big Chip có nhiều lõi hơn, nên việc liên lạc giữa các nhân này sẽ ảnh hưởng lớn đến mức độ cộng tác giữa các lõi. Chính vì vậy, một thiết kế kiến trúc phù hợp cho các chip này sẽ tác động lớn đến hiệu năng.

“Con chip này sẽ sử dụng kiến trúc dạng tile có thể mở rộng. Bộ xử lý này chứa 16 chiplet. Trong mỗi chiplet lại có 16 bộ xử lý CPU được kết nối với nhau thông qua một mạng lưới tích hợp. Mỗi tile này lại được liên kết đối xứng với một tile khác để tạo nên giao tiếp giữa các chiplet với nhau.” Ông Han cho biết trong tài liệu.

“Ngoài ra bộ xử lý này lại sử dụng hệ thống bộ nhớ hợp nhất, điều này có nghĩa bất kỳ nhân trên bất kỳ tile nào cũng được truy cập trực tiếp vào bộ nhớ RAM trên toàn bộ bộ xử lý.“

Giải pháp chế tạo các bộ xử lý khổng lồ theo cách tiếp cận WSI này sẽ giúp Trung Quốc vượt qua được các trở ngại về công nghệ quang khắc, năng suất chế tạo cũng như chi phí sản xuất chip, nhưng vẫn tạo ra được các bộ xử lý đủ năng lực tính toán hiệu suất cao cho siêu máy tính và xử lý tác vụ AI.

Chip AI Wafer-Scale Engine của hãng Cerebras giới thiệu năm 2019 cũng đi theo cách tiếp cận tương tự, tạo ra một con chip khổng lồ thay vì thu nhỏ kích thước đến mức tối đa

Cerebras System, một startup về chip AI của Mỹ, cũng sử dụng cách tiếp cận này để tạo ra các bộ xử lý AI khổng lồ. Năm 2019, Cerebras giới thiệu WSE-1 (Wafer-Scale Engine-1) và năm 2021, họ giới thiệu phiên bản kế tiếp có tên Wafer-Scale Engine-2. Mỗi con chip được bán với giá hàng triệu USD.

Mặc dù giải pháp “Big Chip” mang lại khả năng tính toán mạnh mẽ, nhưng nó cũng đối mặt với những thách thức như vấn đề hiệu suất, làm mát và tỷ lệ hư hỏng. Ông Han cho biết trong nghiên cứu của mình: “Tạo ra các chip khổng lồ rất phức tạp và rất khó để làm nó luôn hoàn hảo do nhiều yếu tố tác động. Cho dù có nhiều cách để cải thiện, chúng có thể khá tốn kém.”

Nguồn tin: https://genk.vn/bi-han-che-cong-nghe-trung-quoc-chon-giai-phap-nguoc-doi-de-phat-trien-chip-cho-sieu-may-tinh-va-ai-20240119122402866.chn